# ELECTRICAL ENGINEERING DEPARTMENT COMPUTER ENGINEERING AND SYSTEMS BRANCH 2ND YEAR FINAL EXAM OF 1ST SEMESTER 2020 - 2021 MICROPROCESSOR SYSTEMS ICODE NO. ECS 20061

The maximum mark for the examination paper is 60 marks, and the mark obtainable for each part of a question is shown in brackets alongside the question.

Instructions to the candidates:

Please use a pen or heavy pencil to ensure legibility.

## QUESTION NUMBER ONE [25 MARKS]

1. What are the main differences between the microcontroller and microprocessor?

[5 Marks]

2. Answer the following questions:

[8 Marks]

- a) Fill in the missing numbers in the following physical address pair: 1775: 777B=72AC?

- b) What is the range of numbers which can be represented by 8 bits if we are representing two's complement integers (express as the formula and as decimal numbers)?

- c) Give the possible values of the 8-bit binary number N which when added to 8-bit number 47H, most significant bit [MSB] equal to "1" and we have no overflow.

- d) What would be the offset address required to point to a destination operand stored at address OO2C3<sub>H</sub> if the contents of the corresponding segment register are OO2A<sub>H</sub>?

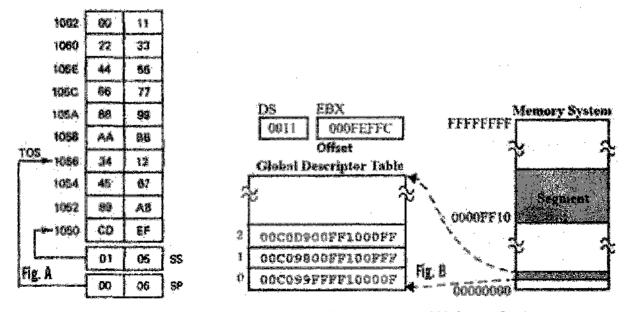

- 3. Assume that stack is in the state shown in Fig. [A], and that the instruction POP AX and POP BX are executed in that order. What value would be popped from stack? Into which register would it be popped? What is new address of the top of stack?

[5 Marks]

4. For a Core2 descriptor that contains a base of 00280000<sub>H</sub>, a limit of 00010<sub>H</sub>, and G=1, what starting and ending locations are addressed by this descriptor? After that, use the descriptor definition to decode the appropriate descriptor shown in Fig. [B].

[7 Marks]

## QUESTION NUMBER TWO [35 MARKS]

1. Answer the following questions:

115 Marks I

- a) The instruction MOV BL, AL stands for move the byte contents from source register AL to destination register BL. Show how to encode the instruction in machine code. The opcode for move operation is 100010.

- b) The instruction ADD AX, [SI] stands for add the 16-bit contents of the memory location indirectly specified by SI to the contents of AX. Encode the instruction in machine code. The opcode for add is 000000.

- c) What is the machine code for the instruction XOR CL, [1234<sub>H</sub>]. This instruction says to exclusive-OR the byte of data at memory address 1234<sub>H</sub> with the byte contents of CL. The opcode for exclusive-OR is 001100.

- d) The instruction ADD [BX+DI+I234<sub>H</sub>], AX means add the word contents of AX to the contents of the memory location specified by based-indexed addressing mode. The opcode for the add operation is 0000000.

- e) The instruction MOV WORD PTR [BP+DI+1234<sub>H</sub>], OABCD<sub>H</sub> says to move the immediate data word ABCD<sub>H</sub> into the memory location specified by based-indexed addressing mode. The opcode for immediate addressing MOV instruction is 1100011 W while, byte 2 has the form of [MOD, OOO, R/M]. Express the instruction in machine code.

- 2. Using paging mechanism, convert the given linear address FF1C3FFE<sub>H</sub> to the corresponding physical address. Note that, the content of CR0 = 8000FC2A<sub>H</sub> and CR3: 00003AFB<sub>H</sub>.

Page table directory Page table 4KB memory page 00110EF3 00003FFC 0003F003 00F3C70E 00110FFF 00100FFF 0011DAC1 00003FF8 0003E003 00F3C70D 00110FFE 00008000 00003FF4 0003D003 00003FF0 0003C003 0003C70E 00112003 00110002 000EF003 00002000 00112003 0003C70D 00111003 00110FFE 10001100 0003C70C 00110003 000C9000 00002008 00111009 000110000 00002004 00110003 00002000 00003003

3. Answer the following questions:

[8 Marks]

[8 Marks]

- a) The six segment registers on the Pentium each have a programmer invisible "cache" register associated with them. What is the purpose of this cache?

- b) What is the purpose of bus interface unit?

- c) Which flag decides whether address for a string operation is incremented or decremented?

- d) What is the result of executing the following instruction: LDS SI,  $[200_H]$  (Hint: DS =  $1200_H$ )?

- 4. Assuming that register BX contains OO3A<sub>H</sub>, what is the result of executing the following instruction: NEG BX

[2 Marks]

5. Assume that prior to execution of the instruction, CL=04, BX=1234<sub>H</sub>, and CF=0. What is the result in BX and CF after execution of the following instruction: RCR BX, CL

[2 Marks]

| 32-bit mode selected R/M |                |           |            |     | 16-bit mode selected R/M |         |            |             |       |

|--------------------------|----------------|-----------|------------|-----|--------------------------|---------|------------|-------------|-------|

| MOD                      | 00             | 01        | 10         | 11  |                          | řeń     | ns:        | 10          | 101_3 |

| R/M                      | VNA            |           |            | W=O | W=1                      | M       | 01         | 10          | W=1   |

| 000                      | EAX            | EAX+d8    | EAX + #32  | AL  | EAX                      | [EX+31] | [BX+51+d8] | [BX+SI+d16] | AX    |

| 001                      | ECX            | ECX+d8    | ECX+d32    | CL  | ECX                      | [EX+DI] | [BX+DI+d8] | [8X+01+06]  | CX    |

| 010                      | EDX            | EDX+d8    | EOX+432    | DL  | EDX                      | [BP+SI] | [BP+SI+d8] | [8P+SI+d16] | DX.   |

| 011                      | EBX            | EBX+d8    | EBX+432    | BL  | EBX                      | (BP+01) | [BP+DI+d8] | [BP+01+d6]  | EX    |

| 100                      | Scale<br>index | Scale +d8 | Scale +d32 | AH  | ESP                      | [SI]    | [5]+d8]    | [SI+#16]    | SP    |

| 101                      | <b>d32</b>     | EPB+48    | EPB+d32    | CH  | EBP                      | [01]    | [DI+d8]    | [01+416]    | BP    |

| 110                      | ESI            | ESI+d8    | ESI+d32    | DH  | ESI                      | di6     | [BP+d8]    | [89+416]    | SI    |

| 111                      | EDI            | EDI+d8    | EOI+432    | BH  | EDI                      | [BX]    | [8X+48]    | [BX+d18]    | DI    |

### 80386/80486/Pentium/Pentium Pro descriptor

| Base<br>881    | G<br>824 | D | ٥ | A<br>V | Limit<br>L19 L16 | Access Rights | Basé<br>823 8 | 16 |  |

|----------------|----------|---|---|--------|------------------|---------------|---------------|----|--|

| Base<br>Brs Bu |          |   |   |        |                  | Limit Lo      |               |    |  |

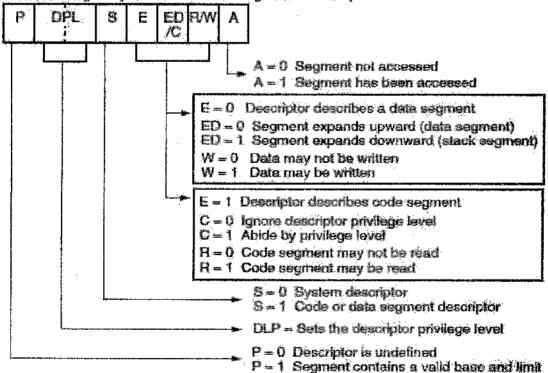

The access rights byte for the 80286 through Core2 descriptor.

#### Segment register prefix override

| 1919:4944.1914  |     |     |     |    | and the second |     |

|-----------------|-----|-----|-----|----|----------------|-----|

| Segment Reg.    | ES  | CS  | SS  | DS | FS             | 63  |

| Prefix Override | 26H | 2EH | 36H | ŒH | <b>64H</b>     | 65H |

The scaled-index byte

|                   |            | * *  |

|-------------------|------------|------|

| 8 8               | index      | Base |

| 1 - : -           | . Street 1 | 1 1  |

| Burgaran estangua |            |      |