## ELECTRICAL ENGINEERING DEPARTMENT COMPUTER ENGINEERING AND SYSTEMS BRANCH 2<sup>ND</sup> YEAR FINAL EXAM OF 2<sup>ND</sup> SEMESTER 2017 - 2018 MICROPROCESSOR SYSTEMS [CODE NO. ECS 2006]

The maximum mark for the examination paper is 60 marks, and the mark obtainable for each part of a question is shown in brackets alongside the question.

Instructions to the candidates:

- Clarify your answer with the suitable sketches as you can.

- Please use a pen or heavy pencil to ensure legibility.

- Please attempt all questions.

## QUESTION NUMBER ONE [20 MARKS]

Briefly illustrate by means of a circuit diagram the working of DRAM. Then, explain how DRAM refreshment is performed? After that, explain how FAMOS and FLOTOX memory devices differ.

[6 Marks]

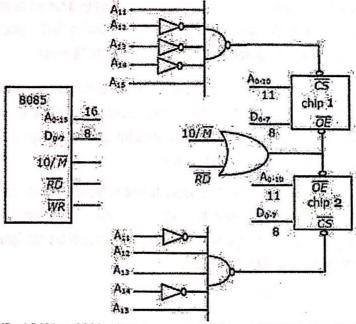

- 2. The following figure shows the memory circuit of 8085 microprocessor.

- a) What is the total size of the memory in the circuit?

- b) What are the beginning and ending addresses of the memory chips?

- c) How will you replace the two NAND gates in the circuit with one 3 to 8 decoder without changing the memory size or the memory addresses? Assume that the decoder has one active high enable E1 and one active low enable E2.

[6 Marks]

3. Interface 16 KB of RAM to 8086 microprocessor starting at 00000H. Two kinds of chips available are 2KB (4 chips) and 4KB (2 Chips).

[8 Marks]

Turn the page to see the rest of the questions

28 May 2018

10:00 AM

Page 1

## QUESTION NUMBER TWO [20 MARKS]

1. A computer uses a memory unit with 256K words of 32 bits each. A binary instruction code is stored in one word of memory. The instruction has four parts: an indirect bit, an operation code, a register code part to specify one of 64 registers, and an address part. Draw the instruction word format and indicate the number of bits in each part? How many bits are there in the data inputs of the memory?

[4 Marks]

- 2. Explain why each of the following micro-operations cannot be executed during a single clock pulse. Specify a sequence of micro-operations that will perform the operation.

- a)  $IR \leftarrow M[PC]$

- b)  $AC \leftarrow AC + TR$

- c)  $DR \leftarrow DR + AC$  (AC does not change)

[5 Marks]

3. What are the two instructions needed in the basic computer to set the E flip-flop to 1?

[2 Marks]

Show the complete logic of the interrupt flip-flops R in the basic computer. Use a JK flip-flop and minimize the number of gates.

[5 Marks]

5. Show the gate structure associated with the control inputs of AR.

[4 Marks]

## QUESTION NUMBER THREE [20 MARKS]

Explain how with some hardware modification it is possible to expand the INTR pin, so that

it accepts seven interrupt request signals. Then, please design a circuit to implement

a hardware interrupt for the interrupt vector type F7<sub>H</sub> (including INTR signal request,

INTA output signal and a buffer 74LS244 to pass F7<sub>H</sub> to DATA lines).

[6 Marks]

2. Does the INTA signal activate for the NMI pin? List the events that occur when a protected mode interrupt becomes active. In your answer, I expect to know how the task state segment is addressed. Afterward, describe the function of trap flag and then, write a procedure that disable trapping feature.

[8 Marks]

3. Briefly illustrate the working operation of power failure detection circuit that causing NMI interrupt when AC power drop out. As a final point, write down with proper diagrams an explanatory note on expanding the interrupt structure of the microprocessor by using 82S9A programmable interrupt controller.

[6 Marks]

```

AR \leftarrow PC

Fetch

R'To:

IR \leftarrow M[AR], PC \leftarrow PC + 1

R'T:

Decode

R'T:

D_0, \ldots, D_7 \leftarrow \text{Decode } IR(12-14),

AR \leftarrow IR(0-11), I \leftarrow IR(15)

Indirect

D'IT;

AR \leftarrow M[AR]

Interrupt:

T_0^*T_1^*T_2(IEN)(FGI + FGO):

R \leftarrow 1

RTo:

AR \leftarrow 0, TR \leftarrow PC

M[AR] \leftarrow TR, PC \leftarrow 0

RT:

RT :

PC \leftarrow PC + 1, IEN \leftarrow 0, R \leftarrow 0, SC \leftarrow 0

Memory-reference:

AND

DoT :

DR \leftarrow M[AR]

DoTs:

AC \leftarrow AC \land DR, SC \leftarrow 0

ADD

D_1T

DR \leftarrow M[AR]

DITS:

AC \leftarrow AC + DR, E \leftarrow C_{out}, SC \leftarrow 0

LDA

D_2T

DR \leftarrow M[AR]

AC\leftarrow DR, SC\leftarrow 0

D2T5:

STA

D_3T_4:

M[AR] \leftarrow AC, SC \leftarrow 0

DAT :

BUN

PC \leftarrow AR, SC \leftarrow 0

BSA.

D.T.

M[AR] \leftarrow PC, AR \leftarrow AR + 1

D_5T_5:

PC \leftarrow AR, SC \leftarrow 0

ISZ

DATA:

DR \leftarrow M[AR]

D_6T_5:

DR \leftarrow DR + 1

M[AR] \leftarrow DR, if (DR = 0) then (PC \leftarrow PC + 1), SC \leftarrow 0

DoTo:

Register-reference:

D_1 l' T_1 = r (common to all register-reference instructions)

IR(i) = B, (i = 0, 1, 2, ..., 11)

SC -0

T:

CLA

B.

AC \leftarrow 0

CLE

rB10:

E \leftarrow 0

AC \leftarrow \overline{AC}

CMA

rB9:

CME

E \leftarrow E

rBa:

CIR

rB7:

AC \leftarrow \text{shr } AC, AC(15) \leftarrow E, E \leftarrow AC(0)

CIL

rB6:

AC \leftarrow shl\ AC,\ AC(0) \leftarrow E,\ E \leftarrow AC(15)

INC

rBs:

AC \leftarrow AC + 1

SPA

If (AC(15) = 0) then (PC \leftarrow PC + 1)

rB.

If (AC(15) = 1) then (PC \leftarrow PC + 1)

SNA

rB:

SZA

If (AC = 0) then PC \leftarrow PC + 1

rB.

SZE

rB_1: If (E=0) then (PC \leftarrow PC+1)

HLT

rBo: S←0

Input-output:

D_i T_i = p (common to all input-output instructions)

IR(i) = B_i (i = 6, 7, 8, 9, 10, 11)

p:

SC \leftarrow 0

INP

AC(0-7) \leftarrow INPR, FGI \leftarrow 0

pB_{11}:

OUT

OUTR \leftarrow AC(0-7), FGO \leftarrow 0

pB10:

SKI

If (FGI = 1) then (PC \leftarrow PC + 1)

pBg:

SKO

pB.

If (FGO = 1) then (PC \leftarrow PC + 1)

ION

IEN ←1

pB7:

IOF

pB6:

IEN ←0

```